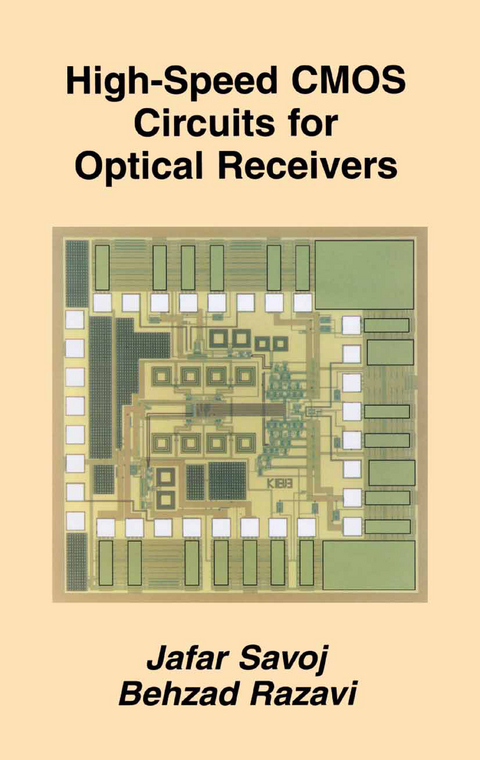

High-Speed CMOS Circuits for Optical Receivers

Seiten

2013

|

Softcover reprint of the original 1st ed. 2001

Springer-Verlag New York Inc.

978-1-4757-7449-8 (ISBN)

Springer-Verlag New York Inc.

978-1-4757-7449-8 (ISBN)

With the exponential growth of the number of Internet nodes, the volume of the data transported on the backbone has increased with the same trend. Different solutions at both the system and the circuit levels have been proposed to increase the data rate of the backbone.

With the exponential growth of the number of Internet nodes, the volume of the data transported on the backbone has increased with the same trend. The load of the global Internet backbone will soon increase to tens of terabits per second. This indicates that the backbone bandwidth requirements will increase by a factor of 50 to 100 every seven years. Transportation of such high volumes of data requires suitable media with low loss and high bandwidth. Among the available transmission media, optical fibers achieve the best performance in terms of loss and bandwidth. High-speed data can be transported over hundreds of kilometers of single-mode fiber without significant loss in signal integrity. These fibers progressively benefit from reduction of cost and improvement of perf- mance. Meanwhile, the electronic interfaces used in an optical network are not capable of exploiting the ultimate bandwidth of the fiber, limiting the throughput of the network. Different solutions at both the system and the circuit levels have been proposed to increase the data rate of the backbone. System-level solutions are based on the utilization of wave-division multiplexing (WDM), using different colors of light to transmit s- eral sequences simultaneously. In parallel with that, a great deal of effort has been put into increasing the operating rate of the electronic transceivers using highly-developed fabrication processes and novel c- cuit techniques.

With the exponential growth of the number of Internet nodes, the volume of the data transported on the backbone has increased with the same trend. The load of the global Internet backbone will soon increase to tens of terabits per second. This indicates that the backbone bandwidth requirements will increase by a factor of 50 to 100 every seven years. Transportation of such high volumes of data requires suitable media with low loss and high bandwidth. Among the available transmission media, optical fibers achieve the best performance in terms of loss and bandwidth. High-speed data can be transported over hundreds of kilometers of single-mode fiber without significant loss in signal integrity. These fibers progressively benefit from reduction of cost and improvement of perf- mance. Meanwhile, the electronic interfaces used in an optical network are not capable of exploiting the ultimate bandwidth of the fiber, limiting the throughput of the network. Different solutions at both the system and the circuit levels have been proposed to increase the data rate of the backbone. System-level solutions are based on the utilization of wave-division multiplexing (WDM), using different colors of light to transmit s- eral sequences simultaneously. In parallel with that, a great deal of effort has been put into increasing the operating rate of the electronic transceivers using highly-developed fabrication processes and novel c- cuit techniques.

TIAs and Limiters.- Clock and Data Recovery Architectures.- A CMOS Interface for Detection of 1.2-Gb / s RZ Data.- A 10-Gb/s Linear Half-rate CMOS CDR Circuit.- A 10-Gb/s CMOS CDR Circuit with Wide Capture Range.- Conclusion.

| Erscheint lt. Verlag | 16.3.2013 |

|---|---|

| Zusatzinfo | XIV, 124 p. |

| Verlagsort | New York, NY |

| Sprache | englisch |

| Maße | 155 x 235 mm |

| Themenwelt | Mathematik / Informatik ► Informatik |

| Technik ► Elektrotechnik / Energietechnik | |

| ISBN-10 | 1-4757-7449-4 / 1475774494 |

| ISBN-13 | 978-1-4757-7449-8 / 9781475774498 |

| Zustand | Neuware |

| Haben Sie eine Frage zum Produkt? |

Mehr entdecken

aus dem Bereich

aus dem Bereich

den digitalen Office-Notizblock effizient nutzen für PC, Tablet und …

Buch | Softcover (2023)

Markt + Technik Verlag

9,95 €