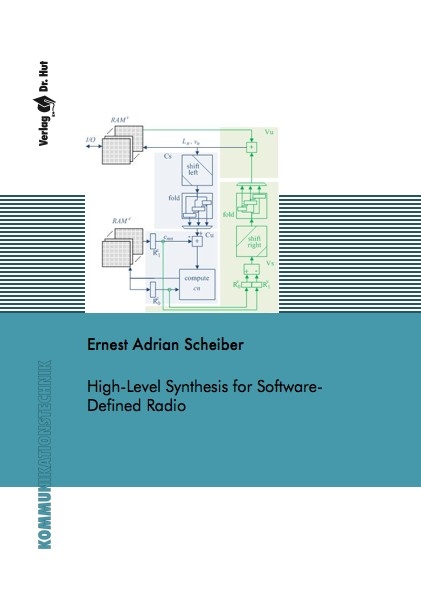

High-Level Synthesis for Software-Defined Radio

Seiten

2017

Dr. Hut (Verlag)

978-3-8439-2986-8 (ISBN)

Dr. Hut (Verlag)

978-3-8439-2986-8 (ISBN)

- Keine Verlagsinformationen verfügbar

- Artikel merken

Die exponentielle Zunahme der Integrationsdichte von integrierten Schaltungen hat eine breite Vielfalt von Applikationen ermöglicht. Diese haben eine technische, wissenschaftliche und gesellschaftliche Revolution bewirkt, die das gegenwärtige Zeitalter maßgeblich kennzeichnet. Die Kehrseite dieser Evolution der Integrationsdichte ist die technische Herausforderung, die der Entwurf der möglichen komplexen Systeme darstellt.

Software-Defined Radio (SDR) benennt ein Entwurfsmuster von flexiblen, programmierbaren, multiband- und multistandard-fähigen Funkgeräten. Komplexe System-on-Chips (SoC) dienen als Prozessierungsplatform für SDR Funkgeräte. SoCs kombinieren allgemeine Mehrzweck-Prozessoren mit spezialisierten Koprozessoren, um eine möglichst optimale Platform bezüglich Flexibilität und Verlustleistung darzubieten.

High-Level Synthese ist die automatische Umsetzung einer funktionellen Beschreibung einer digitalen Schaltung in ein Modell, beschrieben in einer Hardwarebeschreibungssprache, und gilt allgemein als der nächste evolutionäre Schritt zur Steigerung der Produktivität des Entwurfs von digitalen Schaltungen.

Die vorliegende Dissertation untersucht die HLS-Entwurfsmethodik, angewandt auf den Entwurf von Koprozessoren mit Anwendung für SDR. Der Entwurf eines LDPC-Decodierers für IEEE 802.11 und eines Turbo-Decodierers für 3GPP LTE wird dokumentiert.

Die Ergebnisse bezüglich Datendurchsatz, Resourcenanforderungen und Bitfehlerverhältnis werden berichtet. Originäre Beiträge zum Entwurf der Decodierer, die im Rahmen dieser Dissertation entstanden sind die folgenden: ein Mechanismus für Überlaufschutz bei der Vorwärts- und Rückwärtsberechnung der Trellistzustände beim Turbo Decodierer und eine seriell-parallele Schiebeschaltung eingesetzt in den LDPC Decodierer, werden präsentiert. Die HLS-Entwurfsmethodik, sowie ihre Grenzen und potentielle Fehlerquellen werden dargestellt.

Software-Defined Radio (SDR) benennt ein Entwurfsmuster von flexiblen, programmierbaren, multiband- und multistandard-fähigen Funkgeräten. Komplexe System-on-Chips (SoC) dienen als Prozessierungsplatform für SDR Funkgeräte. SoCs kombinieren allgemeine Mehrzweck-Prozessoren mit spezialisierten Koprozessoren, um eine möglichst optimale Platform bezüglich Flexibilität und Verlustleistung darzubieten.

High-Level Synthese ist die automatische Umsetzung einer funktionellen Beschreibung einer digitalen Schaltung in ein Modell, beschrieben in einer Hardwarebeschreibungssprache, und gilt allgemein als der nächste evolutionäre Schritt zur Steigerung der Produktivität des Entwurfs von digitalen Schaltungen.

Die vorliegende Dissertation untersucht die HLS-Entwurfsmethodik, angewandt auf den Entwurf von Koprozessoren mit Anwendung für SDR. Der Entwurf eines LDPC-Decodierers für IEEE 802.11 und eines Turbo-Decodierers für 3GPP LTE wird dokumentiert.

Die Ergebnisse bezüglich Datendurchsatz, Resourcenanforderungen und Bitfehlerverhältnis werden berichtet. Originäre Beiträge zum Entwurf der Decodierer, die im Rahmen dieser Dissertation entstanden sind die folgenden: ein Mechanismus für Überlaufschutz bei der Vorwärts- und Rückwärtsberechnung der Trellistzustände beim Turbo Decodierer und eine seriell-parallele Schiebeschaltung eingesetzt in den LDPC Decodierer, werden präsentiert. Die HLS-Entwurfsmethodik, sowie ihre Grenzen und potentielle Fehlerquellen werden dargestellt.

| Erscheinungsdatum | 16.02.2017 |

|---|---|

| Reihe/Serie | Kommunikationstechnik |

| Verlagsort | München |

| Sprache | englisch |

| Maße | 148 x 210 mm |

| Gewicht | 450 g |

| Themenwelt | Technik ► Elektrotechnik / Energietechnik |

| Schlagworte | High-level synthesis • HLS-Entwurfsmethodik • software-defined radio |

| ISBN-10 | 3-8439-2986-6 / 3843929866 |

| ISBN-13 | 978-3-8439-2986-8 / 9783843929868 |

| Zustand | Neuware |

| Haben Sie eine Frage zum Produkt? |

Mehr entdecken

aus dem Bereich

aus dem Bereich

DIN-Normen und Technische Regeln für die Elektroinstallation

Buch | Softcover (2023)

Beuth (Verlag)

86,00 €

Kolbenmaschinen - Strömungsmaschinen - Kraftwerke

Buch | Hardcover (2023)

Hanser (Verlag)

49,99 €